Study with the several resources on Docsity

Earn points by helping other students or get them with a premium plan

Prepare for your exams

Study with the several resources on Docsity

Earn points to download

Earn points by helping other students or get them with a premium plan

Community

Ask the community for help and clear up your study doubts

Discover the best universities in your country according to Docsity users

Free resources

Download our free guides on studying techniques, anxiety management strategies, and thesis advice from Docsity tutors

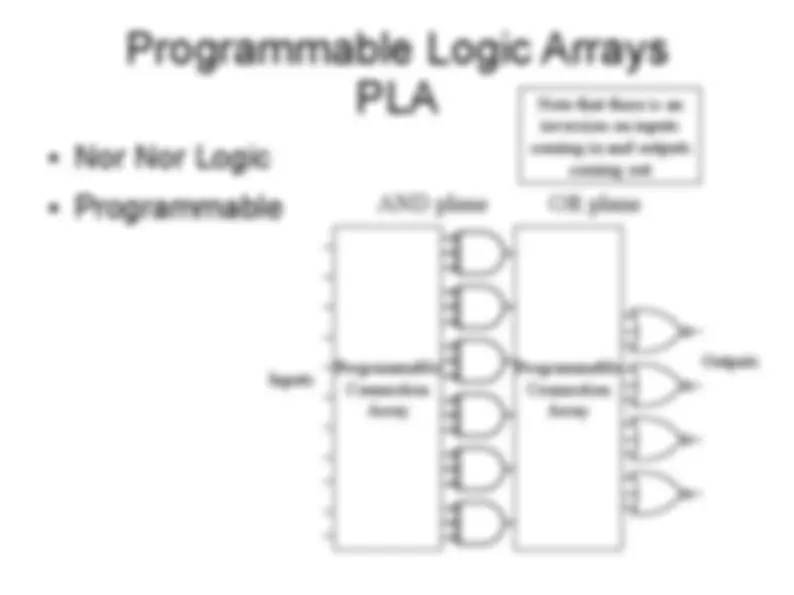

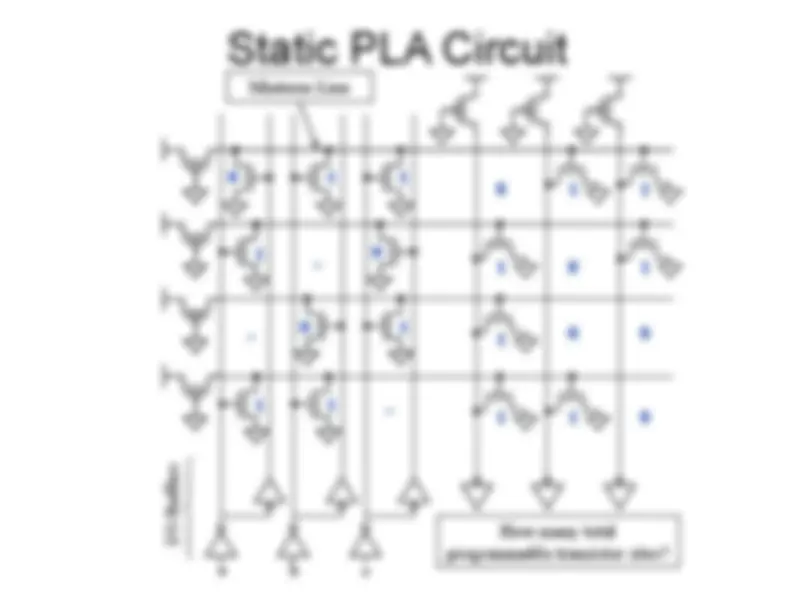

An introduction to programmable logic arrays (plas), focusing on nor nor logic, programmable outputs, and the structure of a pla circuit. It includes a state transition table, a simple nor gate explanation, and a logic minimization process using an example input file.

Typology: Study notes

1 / 9

This page cannot be seen from the preview

Don't miss anything!

R U S1 S0 S1 S0 a b c d

1 - 0 0 0 0 1 0 0 0

R / a

R / a R + U / a

R + U / a

R U ⋅ / b

R U ⋅ / b

R U ⋅ / c

R U ⋅ / d R U ⋅ / c

R U ⋅ / d

R / a

R / a R + U / a

R + U / a

R U ⋅ / b

R U ⋅ / b

R U ⋅ / c

R U ⋅ / d R U ⋅ / c

R U ⋅ / d

.i 4

.o 1

.ilb A B C D

.ob F

0 0 0 0 0

0 0 0 1 0

0 0 1 0 0

0 0 1 1 0

0 1 0 0 0

0 1 0 1 0

0 1 1 0 1

0 1 1 1 1

1 0 0 0 1

1 0 0 1 1 1 0 1 0 0 1 0 1 1 0 1 1 0 0 0 1 1 0 1 0 1 1 1 0 0 1 1 1 1 0 .e

● (^) COMMENTS ABOUT THE INPUT FILE ● (^) .i 4 (Input variables = 4) ● (^) .o 1 (Output variables = 1) ● (^) .ilb A B C D (Input variable names) ● (^) .ob F (Output variable name) ● (^) 0 0 0 0 0 (Truth table row, 4 inputs and output) ● (^) .e (Signifies the end of the input file.)

.i 4

.o 1

.ilb A B C D

.ob F

.p 2

100- 1

011- 1

.e

Interpretation:

.p 2 (Indicates that there are two

terms in the output expression)

100- 1 ( this term is AB'C'. notation: B'

is B inverse, so this is read as A and not B and not C)

011- 1 ( this term is A'BC)