Study with the several resources on Docsity

Earn points by helping other students or get them with a premium plan

Prepare for your exams

Study with the several resources on Docsity

Earn points to download

Earn points by helping other students or get them with a premium plan

Community

Ask the community for help and clear up your study doubts

Discover the best universities in your country according to Docsity users

Free resources

Download our free guides on studying techniques, anxiety management strategies, and thesis advice from Docsity tutors

Material Type: Notes; Class: COMPUTER ARCHITECTURE; Subject: Computer Science; University: Kent State University; Term: Spring 2008;

Typology: Study notes

1 / 56

This page cannot be seen from the preview

Don't miss anything!

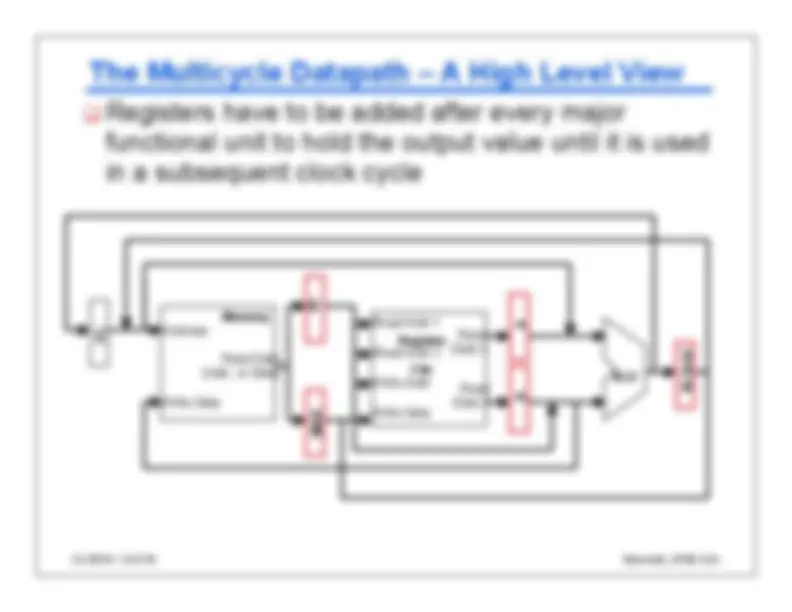

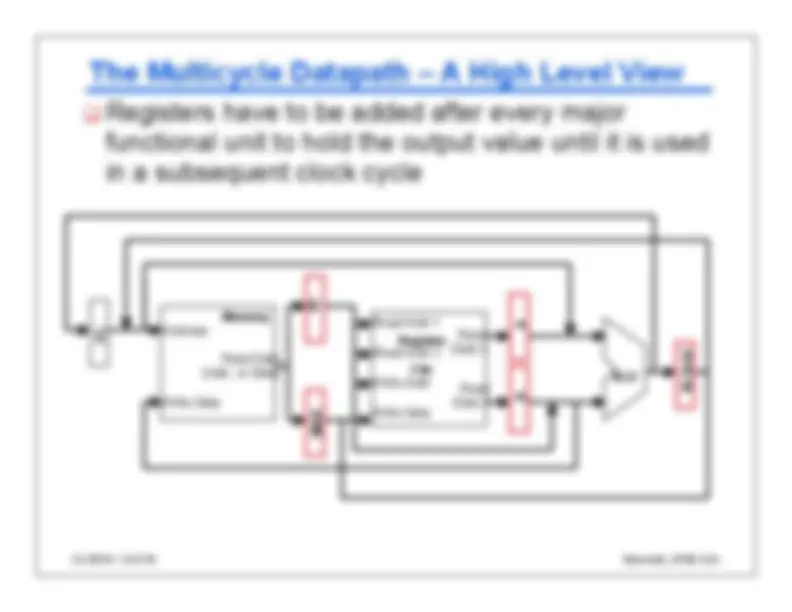

Address Read Data (Instr. or Data) PC^ Memory Write Data

Read Read AddrAddr (^12) Write Addr

Register File Data 1^ Read Write Data Data 2^ Read^ ALU

IR

MDR

A B^ ALUout

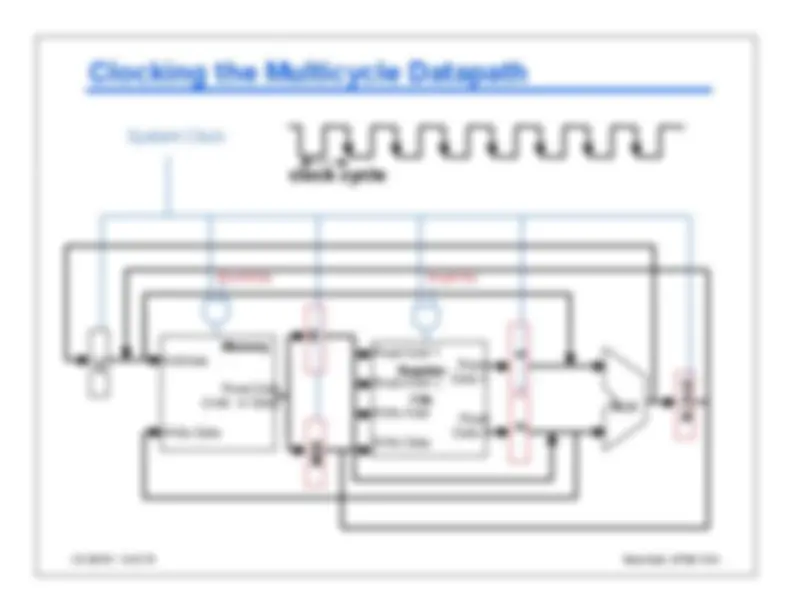

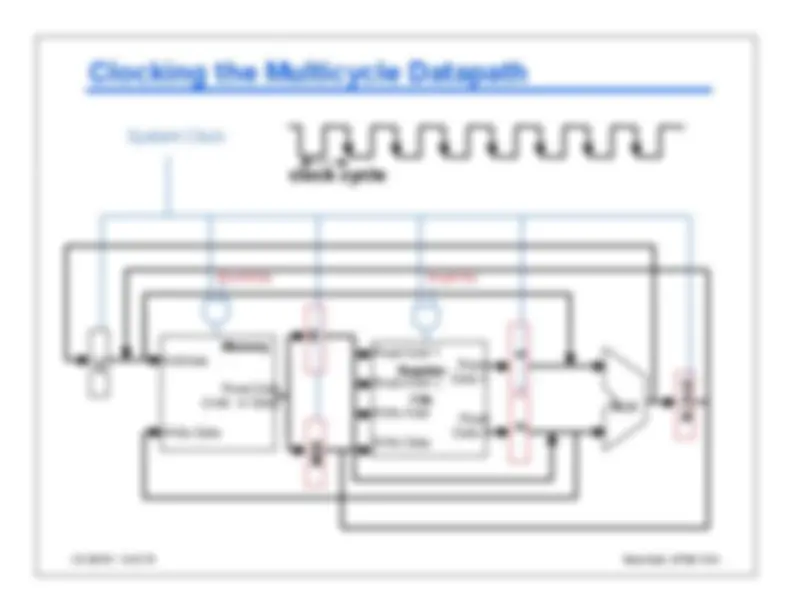

Address Read Data (Instr. or Data) PC^ Memory Write Data

Read Read AddrAddr (^12) Write Addr

Register File Data 1^ Read Write Data Data 2^ Read^ ALU

IR

MDR

A B^ ALUout

MemWrite RegWrite

clock cycle

Address Read Data (Instr. or Data)

PC^ Memory

Write Data

Read Read AddrAddr (^12) Write Addr

Register File Data 1^ Read Write Data Data 2^ Read^ ALU

IR MDR

A B^ ALUout Extend^ Sign left 2^ Shift (^) controlALU

left 2^ Shift

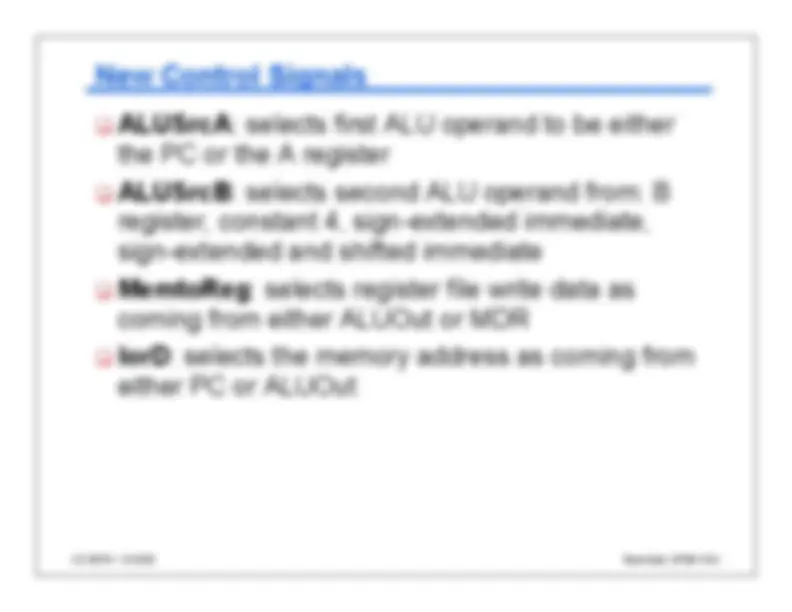

Control^ ALUOp MemWrite MemtoReg IRWrite IorD MemRead^ PCWrite PCWriteCond RegDst^ RegWrite^ ALUSrcA ALUSrcB

zero

PCSource

Instr[5-0]

Instr[25-0]^ PC[31-28]

Instr[15-0]

Instr[31-26]

32

28

Reading from or writing to any of the internal registers, Register File, or the PC occurs (quickly) at the beginning

(for read) or the end of a clock cycle (for write)Reading from the Register File takes ~50% of a clock cycle since it has additional control and access overhead (but reading can be done in parallel with decode) Had to add functional unit input ports (e.g., Memory, ALU) because multiplexors in front of several of the they are now shared by different clock cycles and/or do multiple jobs

All operations occurring in one clock cycle occur in parallel

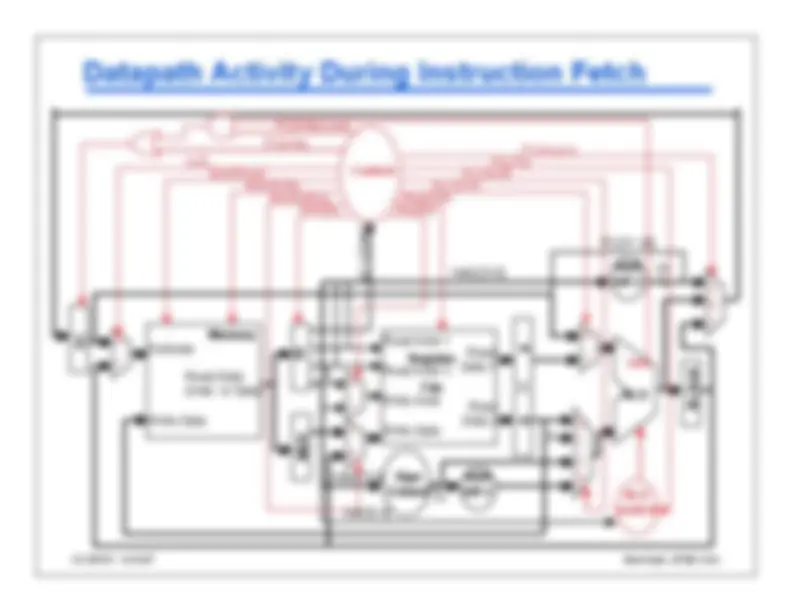

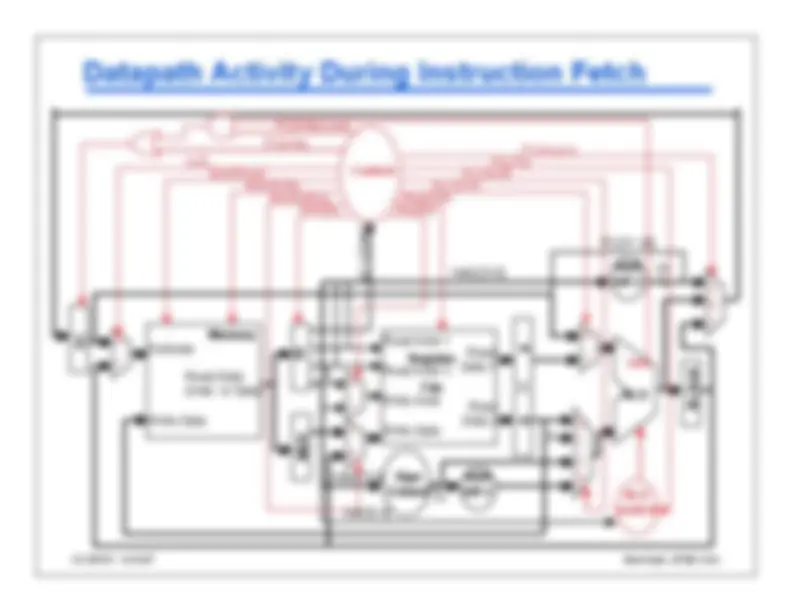

Address Read Data (Instr. or Data)

PC^ Memory Write Data

Read Read AddrAddr (^12) Write Addr

Register File Data 1^ Read Write Data Data 2^ Read^ ALU

IR MDR

A B^ ALUout Extend^ Sign left 2^ Shift (^) controlALU

left 2^ Shift

Control^ ALUOp MemWrite MemtoReg IRWrite IorD MemRead^ PCWrite PCWriteCond RegDst^ RegWrite^ ALUSrcA ALUSrcB

zero

PCSource

Instr[5-0]

Instr[25-0]^ PC[31-28]

Instr[15-0]

Instr[31-26]

32

28

Address Read Data (Instr. or Data)

PC^ Memory Write Data

Read Read AddrAddr (^12) Write Addr

Register File Data 1^ Read Write Data Data 2^ Read^ ALU

IR MDR

A B^ ALUout Extend^ Sign left 2^ Shift (^) controlALU

left 2^ Shift

Control^ ALUOp MemWrite MemtoReg IRWrite IorD MemRead^ PCWrite PCWriteCond RegDst^ RegWrite^ ALUSrcA ALUSrcB

zero

PCSource

Instr[5-0]

Instr[25-0]^ PC[31-28]

Instr[15-0]

Instr[31-26]

32

28

Address Read Data (Instr. or Data)

PC^ Memory Write Data

Read Read AddrAddr (^12) Write Addr

Register File Data 1^ Read Write Data Data 2^ Read^ ALU

IR MDR

A B^ ALUout Extend^ Sign left 2^ Shift (^) controlALU

left 2^ Shift

Control^ ALUOp MemWrite MemtoReg IRWrite IorD MemRead^ PCWrite PCWriteCond RegDst^ RegWrite^ ALUSrcA ALUSrcB

zero

PCSource

Instr[5-0]

Instr[25-0]^ PC[31-28]

Instr[15-0]

Instr[31-26]

32

28

Address Read Data (Instr. or Data)

PC^ Memory Write Data

Read Read AddrAddr (^12) Write Addr

Register File Data 1^ Read Write Data Data 2^ Read^ ALU

IR MDR

A B^ ALUout Extend^ Sign left 2^ Shift (^) controlALU

left 2^ Shift

Control^ ALUOp MemWrite MemtoReg IRWrite IorD MemRead^ PCWrite PCWriteCond RegDst^ RegWrite^ ALUSrcA ALUSrcB

zero

PCSource

Instr[5-0]

Instr[25-0]^ PC[31-28]

Instr[15-0]

Instr[31-26]

32

28