Study with the several resources on Docsity

Earn points by helping other students or get them with a premium plan

Prepare for your exams

Study with the several resources on Docsity

Earn points to download

Earn points by helping other students or get them with a premium plan

Community

Ask the community for help and clear up your study doubts

Discover the best universities in your country according to Docsity users

Free resources

Download our free guides on studying techniques, anxiety management strategies, and thesis advice from Docsity tutors

Material Type: Notes; Professor: Steinfadt; Class: COMPUTER ARCHITECTURE; Subject: Computer Science; University: Kent State University; Term: Spring 2008;

Typology: Study notes

1 / 56

This page cannot be seen from the preview

Don't miss anything!

Taken from Kevin Schaffer’s slides CS 35101 Computer Architecture Spring 2008

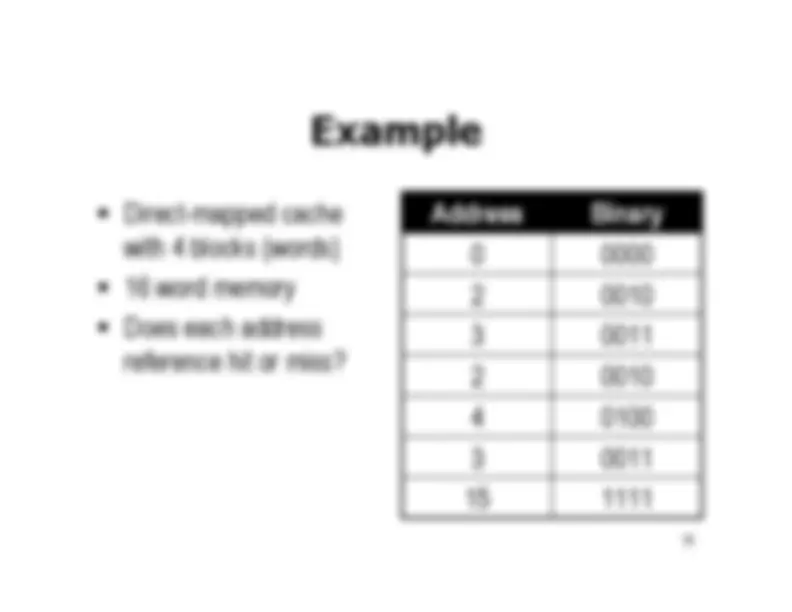

Index V Tag Data 11 N

00 Y 00 Mem[0] Index V Tag Data 11 N 10 Y 00 Mem[2]

00 Y 00 Mem[0] Index V Tag Data 11 Y 00 Mem[3] 10 Y 00 Mem[2]

00 Y 00 Mem[0] Index V Tag Data

11 Y 00 Mem[3] 10 Y 00 Mem[2]

00 Y 00 Mem[0] Index V Tag Data 11 Y 00 Mem[3] 10 Y 00 Mem[2]

00 Y 01 Mem[4] Index V Tag Data 11 Y 00 Mem[3] 10 Y 00 Mem[2]

00 Y 01 Mem[4] Index V Tag Data 11 Y 11 Mem[15] 10 Y 00 Mem[2]

00 Y 01 Mem[4] Index V Tag Data