Study with the several resources on Docsity

Earn points by helping other students or get them with a premium plan

Prepare for your exams

Study with the several resources on Docsity

Earn points to download

Earn points by helping other students or get them with a premium plan

Community

Ask the community for help and clear up your study doubts

Discover the best universities in your country according to Docsity users

Free resources

Download our free guides on studying techniques, anxiety management strategies, and thesis advice from Docsity tutors

dajbsdnaskjndkjasndjasnjkdasndjnaskdnasndkjasndnasjkndjkasdjkasjndkasdasdlasmdlasndkjasnkdjasndjkasnkdnsakdnjkasndjkansdknjkadd

Typology: Thesis

1 / 76

This page cannot be seen from the preview

Don't miss anything!

11

2

Embedded Computing Systems (Cyber-Physical Systems)

Typical SOC Core Sizes 2017/9/27 4

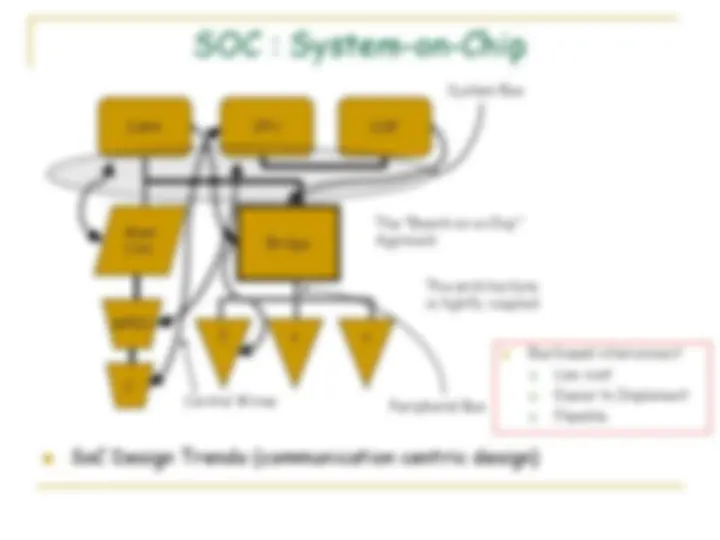

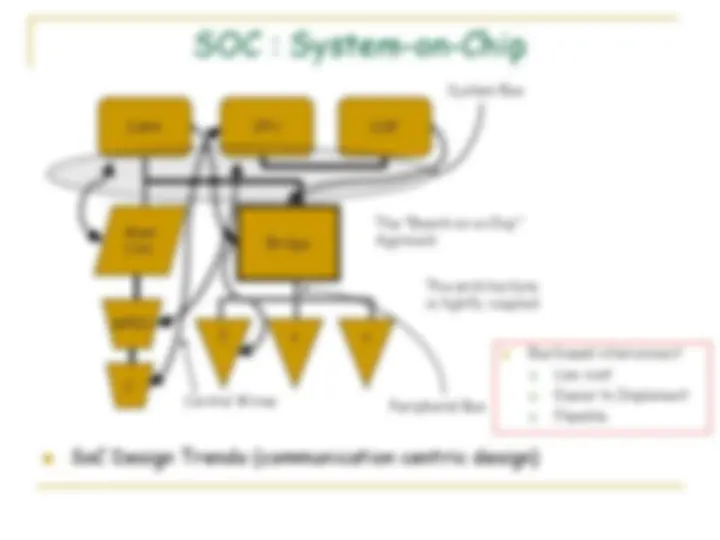

SOC : System-on-Chip SoC Design Trends (communication centric design) The architecture is tightly coupled

Mem Ctrl. Bridge MPEG I o o The “Board-on-a-Chip” Approach C System Bus Control Wires (^) Peripheral Bus Bus based interconnect Low cost Easier to Implement Flexible

Design Representations

8 Performance

10 Variation The extreme variability of the individual devices, up to ±20%. In addition, the device properties often vary between each processed semiconductor wafer. Slight changes to the amount of diffusion time, uneven doping levels, etc. can have large effects on device properties.

11 Variation

1313 Design Methodologies Design Complexity Design Productivity 1975 1980 1985 1990 1995 2000 Gates High level SPICE Pattern Generation IC CAD ASICs Place & Route Logic Simulation Logic Synthesis Behavioral Synthesis Cycle-Based Simulation Design Reuse Deep Submicron System on a Chip Transistors Polygons

1414 System Level Design Investment of People & Money System Level Design Physical Design Functional Design Functional Verification Some will move to: physical design system level Designer population and budgets will shift

1616 A Typical ASIC Design Flow Floorplan Macro placement Signal Integrity Check & repair Timing Driven Routing Timing Driven Placement Physical Libs Pinout Timing Constraints DRC/LVS Mask Data Gen Extraction & Delay Calc STA and/or Timing Simulation sdf Formal Verification

Mask Data to FAB Back-End Part Clock Tree Synthesis

Design Flow Comparison ASIC (^) FPGA

RTL Synthesis Flow 9/27/2017 19

Physical Synthesis Flow 9/27/2017 20