Study with the several resources on Docsity

Earn points by helping other students or get them with a premium plan

Prepare for your exams

Study with the several resources on Docsity

Earn points to download

Earn points by helping other students or get them with a premium plan

Community

Ask the community for help and clear up your study doubts

Discover the best universities in your country according to Docsity users

Free resources

Download our free guides on studying techniques, anxiety management strategies, and thesis advice from Docsity tutors

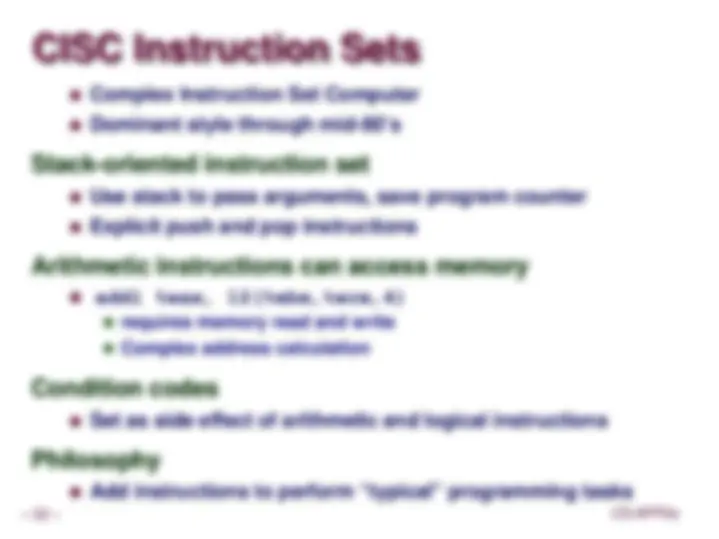

Assembly Language, View Layer of Abstraction, Y86 Processor State, Y86 Instructions, Encoding, Registers Arithmetic and Logical operations, Conditions. Move Instructions . Jump Operation. Subroutine Call and Return State condition. Assembly Y86 Program, CISC Instruction Sets

Typology: Slides

1 / 37

This page cannot be seen from the preview

Don't miss anything!

CS:APP2e

Instructions

Layer of Abstraction Above: how to program machine

Below: what needs to be built

Y86 Instruction Set #

pushl rA A (^0) rA 8 jXX Dest (^7) fn Dest popl rA B (^0) rA 8 call Dest (^8 0) Dest cmovXX rA, rB (^2) fn rA rB irmovl V, rB (^3 0 8) rB V rmmovl rA, D(rB) (^4 0) rA rB D mrmovl D(rB), rA (^5 0) rA rB D OPl rA, rB (^6) fn rA rB ret 9 0 nop 1 0 halt 0 0

Y86 Instructions Format 1 – 6 bytes of information read from memory

Each accesses and modifies some part(s) of the program state

Y86 Instruction Set #

pushl rA A (^0) rA 8 jXX Dest (^7) fn Dest popl rA B (^0) rA 8 call Dest (^8 0) Dest cmovXX rA, rB (^2) fn rA rB irmovl V, rB (^3 0 8) rB V rmmovl rA, D(rB) (^4 0) rA rB D mrmovl D(rB), rA (^5 0) rA rB D OPl rA, rB (^6) fn rA rB ret 9 0 nop 1 0 halt 0 0 addl 6 0 subl 6 1 andl 6 2 xorl 6 3

Y86 Instruction Set #

pushl rA A (^0) rA 8 jXX Dest (^7) fn Dest popl rA B (^0) rA 8 call Dest (^8 0) Dest rrmovl rA, rB (^2) fn rA rB irmovl V, rB (^3 0 8) rB V rmmovl rA, D(rB) (^4 0) rA rB D mrmovl D(rB), rA (^5 0) rA rB D OPl rA, rB (^6) fn rA rB ret 9 0 nop 1 0 halt 0 0 jmp 7 0 jle 7 1 jl 7 2 je 7 3 jne 7 4 jge 7 5 jg 7 6

Instruction Example Addition Instruction Add value in register rA to that in register rB

Set condition codes based on result e.g., addl %eax,%esi Encoding: 60 06 Two-byte encoding

Arithmetic and Logical Operations Refer to generically as “OPl” Encodings differ only by “function code”

Set condition codes as side effect

Move Instruction Examples

Conditional Move Instructions Refer to generically as “cmovXX” Encodings differ only by “function code” Based on values of condition codes Variants of rrmovl instruction

Y86 Program Stack Region of memory holding program data Used in Y86 (and IA32) for supporting procedure calls Stack top indicated by %esp

Stack grows toward lower addresses

Stack Operations Decrement %esp by 4 Store word from rA to memory at %esp Like IA Read word from memory at %esp Save in rA Increment %esp by 4 Like IA

Miscellaneous Instructions Don’t do anything Stop executing instructions IA32 has comparable instruction, but can’t execute it in user mode We will use it to stop the simulator Encoding ensures that program hitting memory initialized to zero will halt

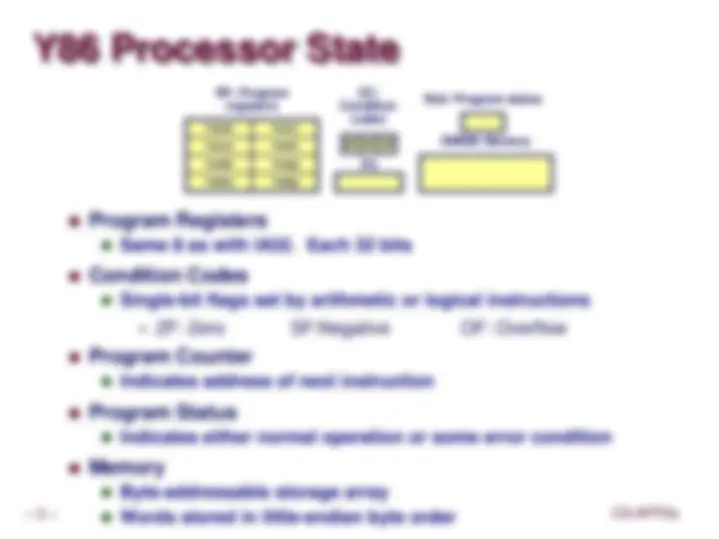

Status Conditions

Normal operation Halt instruction encountered Bad address (either instruction or data) encountered Invalid instruction encountered Desired Behavior If AOK, keep going Otherwise, stop program execution