Study with the several resources on Docsity

Earn points by helping other students or get them with a premium plan

Prepare for your exams

Study with the several resources on Docsity

Earn points to download

Earn points by helping other students or get them with a premium plan

Community

Ask the community for help and clear up your study doubts

Discover the best universities in your country according to Docsity users

Free resources

Download our free guides on studying techniques, anxiety management strategies, and thesis advice from Docsity tutors

Solutions to the midterm exam questions for the cpe/ee 421/521 course offered by the university of alabama in huntsville - ece department. The solutions cover topics such as sequential networks, vhdl descriptions, timing diagrams, and combinational logic. Students can use these solutions to check their understanding of the concepts covered in the exam.

Typology: Exams

1 / 6

This page cannot be seen from the preview

Don't miss anything!

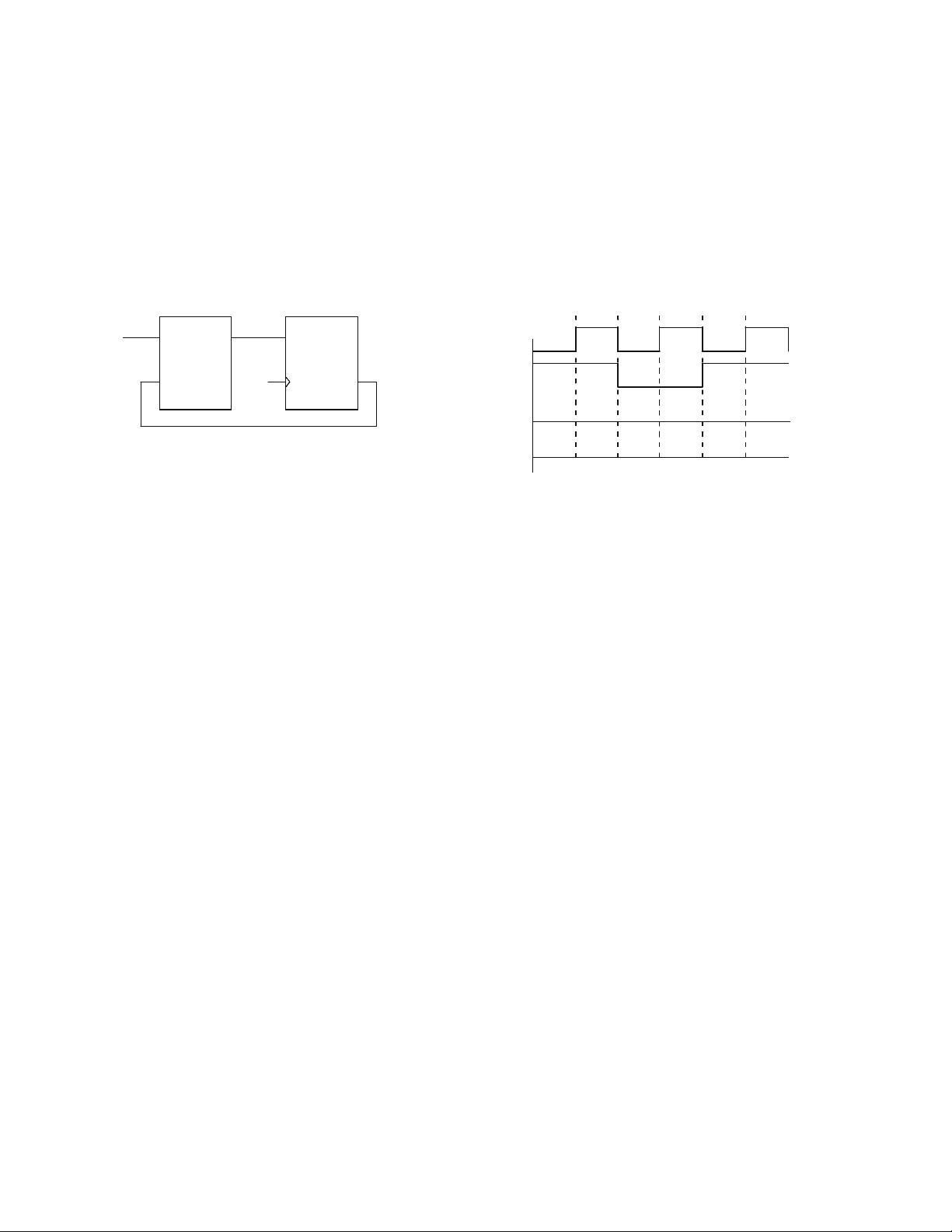

PLA Clk

D

Q

Z X

X

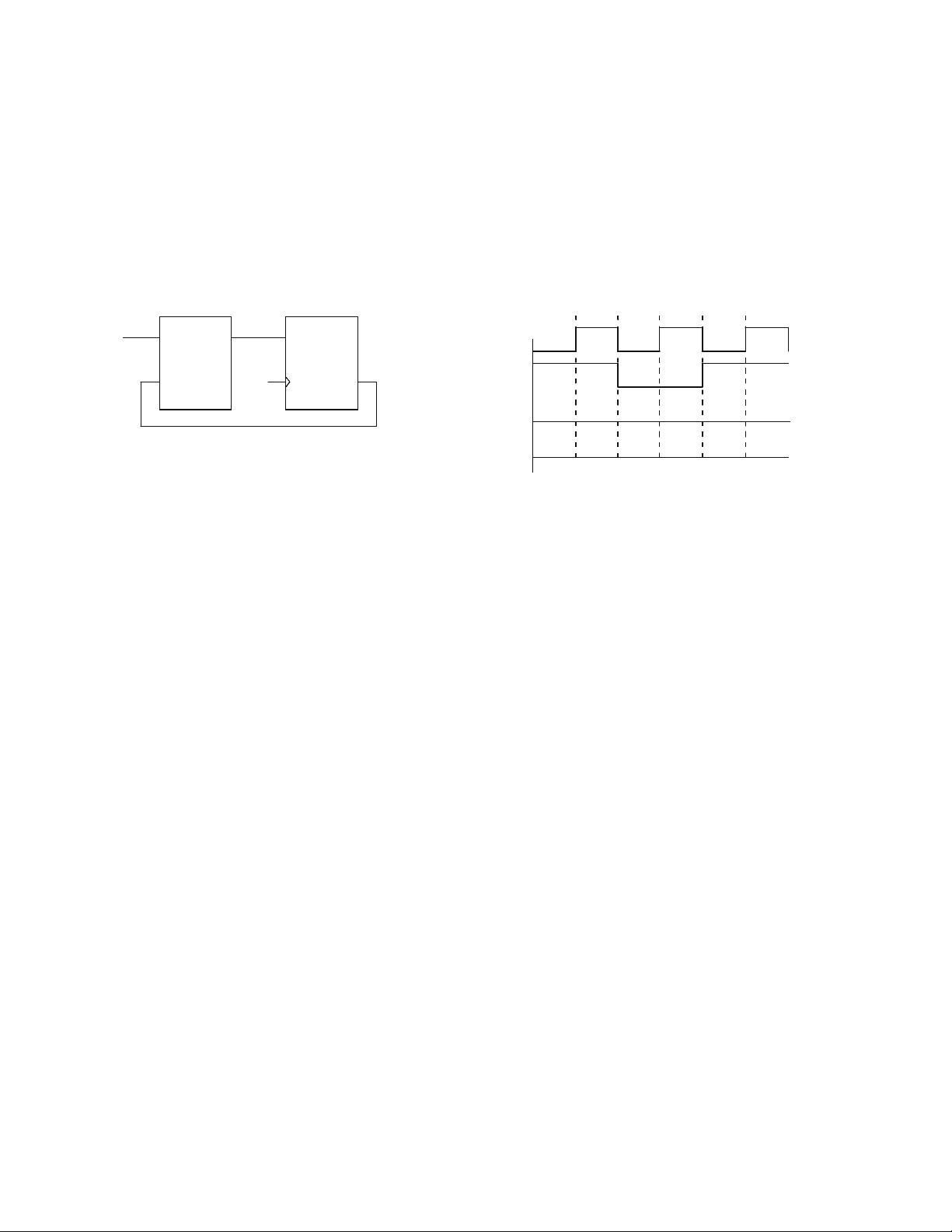

Clk

20 40 60 80 100

Q

Z

For both the setup time and hold time, there are two paths to consider, one from X to the D input of the flip-flop and the other from Q to the D input of the flip-flop. From the timing diagram, tck = 40 ns, tx = 20 ns and ty = 20 ns, where tck is the clock period, tx is the time from a change on X to the active edge of the clock and ty is the time from the active edge of the clock to a change on X. The following equations apply: For Q: (1) t (^) ck ≥ t (^) pdmax + tcmax + tsu , (2) th ≥ t (^) pdmin + tcmin For X: (3) t (^) x ≥ t (^) su + tcmax , (4) t (^) h ≥ t (^) y + tcmin where t (^) pd is the propagation delay through the flip-flop and t (^) c is the propagation delay through the combinational circuit (PLA)

So, for setup, So, for hold, (1) 40 ns ≥ 10 ns + 10 ns + t (^) su , tsu ≤ 20 ns (2) t (^) h ≥ 5 ns + 5 ns, th ≥ 10 ns (3) 20 ns ≥ t (^) su + 10 ns , tsu ≤ 10 ns (4) t (^) h ≥ 20 ns + 5 ns, th ≥ 25 ns

For both the setup and the hold times to be always satisfied, we must take the smaller numbers so t (^) su = th = 10 ns

entity MUX4_1 is port (I3, I2, I1, I0, S1,S0 : in bit; F : out bit); end MUX4_1; architecture MUX4_1of MUX4_1 is begin process (I3, I2, I1, I0, S1, S0) begin if (S1 = ‘0’ and S0 = ‘0’) then F <= I0; elsif (S1 = ‘0’ and S0 = ‘1’) then F <= I1; elsif (S1 = ‘1’ and S0 = ‘0’) then F <= I2; else F <= I3; end if; end MUX4_1;

entity prob is port (D : inout bit); end prob;

architecture PROB of PROB is signal A, B, C, E, F : bit; begin P1: process (A, C) begin B <= A after 3 ns; E <= C after 5 ns; end process P1; C1: C <= A after 10 ns; P2: process (C, E) begin F <= C and E after 4 ns; end process P2; C2: D <= A or B or C or F after 1 ns; end PROB;

A

D

B

C

0 0 0

0 0

(^0 0 )

1

1

1

1

1

1

1 1

I

H

G

F

E

D

C

A B C D E F G

I=B C=I

I=D C=E

I=H C=A

B

H

I=C C=G

I=A

I=A A=B C=I

A=G A=C C=G

I=G

D=E I=C I=E C=F E=H F=A H=A A=C

E=A F=C I

H

G

F

E

D

C

A B C D E F G

I=B C=I

I=D C=E

I=H C=A

B

H

I=C C=G

I=A

I=A A=B C=I

A=G A=C C=G

I=G

D=E I=C I=E C=F E=H F=A H=A A=C

E=A F=C

I

H

G

F

E

D

C

A B C D E F G

I=B C=I

I=D C=E

I=H C=A

B

H

I=C C=G

I=A

I=A A=B C=I

A=G A=C C=G

I=G

D=E I=C I=E C=F E=H F=A H=A A=C

E=A F=C

QF

D

CLK/G

QL

flip-flops, registers and counters in the system.

_in the sensitivity list.

ENTITY state_machine IS PORT (sig_in ; IN BIT; clk : IN BIT; sig_out : OUT BIT); END state_machine;

ARCHITECTURE state_machine OF state_machine IS TYPE state_type IS (a, b, c, d, e); SIGNAL current_state, next_state : state_type; BEGIN PROCESS (sig_in, current_state) BEGIN sig_out <= ‘0’; next_state <= b; CASE current_state WHEN a => IF sig_in = ‘0’ THEN next_state <= e; sig_out <= ‘1’; ELSE next_state <= d; END IF ; WHEN b => IF sig_in = ‘0’ THEN next_state <= b; ELSE next_state <= d; sig_out <= ‘1’; END IF ; WHEN c => IF sig_in = ‘1’ THEN next_state <= a;